Samsung fab cobbling IP offerings for data

- Automotive

- 2023-09-23 21:29:23

Samsung Foundry is on the offense, this time by cobbling IP partnerships to help design engineers build complex system-on-chips (SoCs) for multiple process generations. A broad portfolio of IPs on Samsung’s fab platforms is also expected to help accelerate silicon success in highly demanding SoC designs for artificial intelligence (AI), automotive, high-performance computing (HPC), networking, and storage applications.

These announcements are significant amid the flurry of collaboration activities on the part of Intel Foundry Services (IFS), which has also been in the news for its PowerVia breakthrough, the first backside power delivery mechanism for 2-nm chips, which Intel is expected to make available next year ahead of archrivals TSMC and Samsung Foundry. All the while, TSMC has been going as strong as ever, both on semiconductor manufacturing technology and IP ecosystem frontiers.

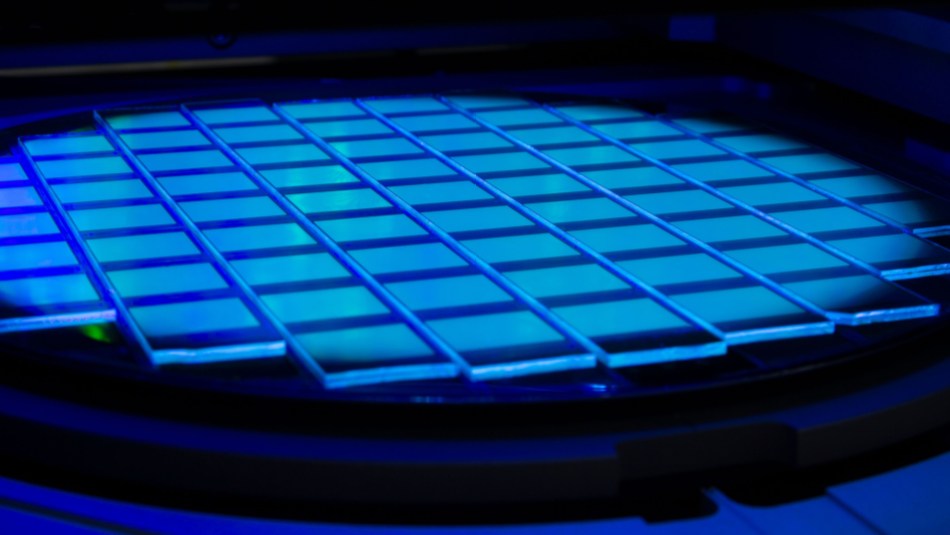

Samsung, the first fab to produce a 3-nm chip and implement gate-all-around (GAA) transistors, is now making its presence felt with the availability of IP offerings through each generation of its process nodes. A rich set of IPs will also be critical in manufacturing high-end SoCs for automotive, mobile, HPC, and multi-die designs.

Below is a brief view of the IP deals that Samsung Foundry has inked in the past few days.

Alphawave Semi has expanded its collaboration with Samsung to add 3-nm connectivity IP to facilitate data-intensive applications such as generative AI and the associated infrastructure required by data centers. The connectivity IP and chiplet portfolio includes 112 Gbps Ethernet and PCI Express Gen6/CXL 3.0 interfaces for SoC designs.

“Data center connectivity is undergoing a remarkable transformation due to the rise of generative AI, ushering in an era of high-performance chiplet-enabled silicon,” said Tony Pialis, CEO and co-founder of Alphawave Semi. Samsung Foundry has already been collaborating with Alphawave Semi on 4-nm and 5-nm process nodes.

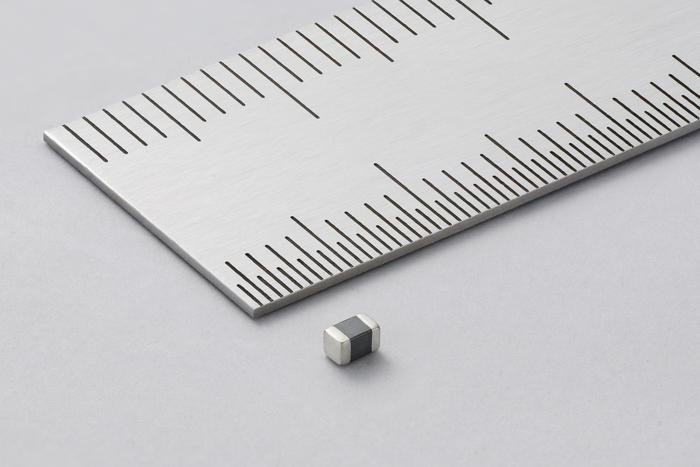

Memory and interface IPsCadence Design Systems has also signed a multi-year agreement with the Korean company to expand the availability of its IP portfolio for Samsung Foundry’s SF5A process, the 5-nm process variant to support automotive applications. The IP offerings include 112/56/25/10G PHY/MAC, PCI Express (PCIe) 6.0/5.0/4.0/3.1 PHY/controller, Universal Chiplet Interconnect Express (UCIe) PHY/controller, USB3.x PHY/controller and a complete PHY and controller offering for GDDR6 and DDR5/4 memory designs.

The collaborative pact is aimed at providing a future-proof migration path for high-performance, high-bandwidth memory interface solutions crucial in designing generative AI/ML, hyperscale, and HPC applications. Moreover, the combo of PHY and controller IP will simplify integration, minimize risks, and enable faster time to market for SoC developers.

IP optimization for automotive nodesSamsung Foundry has also joined hands with Synopsys to bolster IP offerings for its 8LPU, SF5, SF4, and SF3 process nodes. That includes IPs for USB, PCI Express, 112G Ethernet, UCIe, LPDDR, DDR and MIPI as well as foundation IP.

Next, Synopsys will optimize IPs for Samsung’s SF5A and SF4A automotive process nodes to meet stringent Grade 1 and Grade 2 temperature and AEC-Q100 reliability requirements. Additionally, the automotive-grade IP for advanced driver asistance systems (ADAS) chips will include design failure mode and effect analysis (DFMEA) reports, which can save months of development effort for automotive SoCs.

Two important trends

The above partnerships highlight two important trends. First, they underscore the critical importance of IP offerings in the rapidly changing semiconductor ecosystem. A diversified IP portfolio is vital in coping with the inherent challenges of designing chips for advanced chip manufacturing technologies. “It provides designers with a low-risk path to achieving their design requirements and quickly launching differentiated products to the market,” noted John Koeter, senior VP of product management and strategy for IP at Synopsys.

The second trend these partnerships unravel is the increasingly blurring lines between EDA and IP worlds. Two of the three ties-ups with Samsung Foundry involve leading EDA houses. It’ll be interesting to watch how this convergence between EDA and IP worlds evolves as the advanced fabs move toward smaller process nodes.

Related Content

China Struggles to Crack Chip ManufacturingTSMC approaching 1 nm with 2D materials breakthroughA closer look at TSMC’s 3-nm node and FinFlex technologyThe 3-nm fab race: Samsung reportedly nears the finish lineFrom FinFET to GAA: Samsung’s fab journey to 3 nm and 2 nmSamsung fab cobbling IP offerings for data由Voice of the EngineerAutomotiveColumn releasethank you for your recognition of Voice of the Engineer and for our original works As well as the favor of the article, you are very welcome to share it on your personal website or circle of friends, but please indicate the source of the article when reprinting it.“Samsung fab cobbling IP offerings for data”