How physically aware interconnect IP bolsters SoC design

- ICDesign

- 2023-09-23 23:01:38

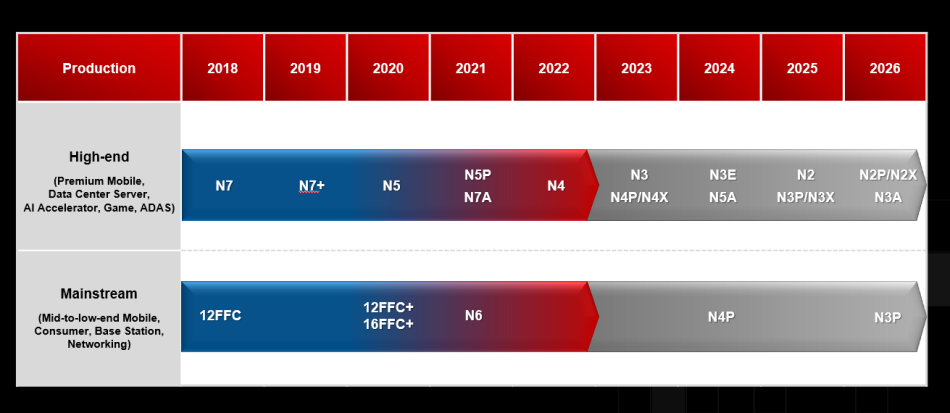

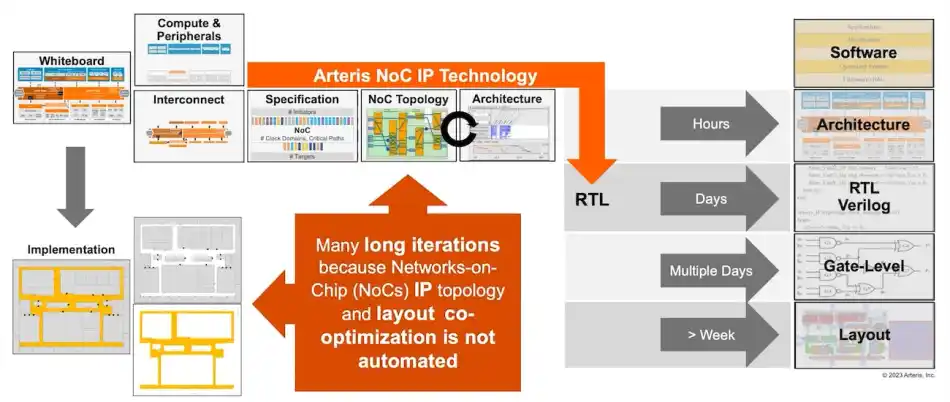

The network-on-chip (NoC) technology, which connects IP blocks in highly complex system-on-chip (SoC) designs, has ascended to the next logical level by becoming physically aware. According to Andy Nightingale, VP of product marketing at Arteris, that accelerates the exploration of the needed space to achieve an optimal NoC topology at the front-end and speeds up timing closure at the back-end.

Arteris has unveiled its next-generation interconnect IP, FlexNoC 5, which it calls the first physically aware NoC technology. It’s aimed to allow SoC architecture teams, logic designers, and integrators to incorporate physical constraint management and achieve faster physical convergence over manual refinements with fewer iterations from the layout team.

Figure 1 A large 7-nm SoC may require 6,000+ pipeline registers and performing the insertion of pipeline registers by hand invariably results in overdesign. Source: Arteris

Currently, IC designers use manual workflows that typically include numerous iterations of pipeline insertions, effort-intensive creation of constraints for physical placement of units, and lengthy NoC placement plus route iterations to converge on the power, performance, and area (PPA) targets for SoC designs. Here, a physically aware interconnect IP shortens the duration of various manual steps while eliminating the iterations.

Graham Curren, CEO of Sondrel, acknowledges that physical constraints have always been an important issue and are even more important below 16-nm geometries. Sondrel, a supplier of IC design services, has employed FlexNoC 5 in its custom SoC design project, and according to Curren, that has enabled RTL teams to verify that architectures meet physical constraints and provide a better starting point for place and route.

Charles Janac, president and CEO of Arteris, added that without physical awareness, IC developers might end up with SoC architectures that are difficult or even impossible to place and route. “That may result in multiple turns, overall project delay risks, and additional project costs, particularly for geometries of 16 nm and below.”

Figure 2 FlexNoC 5 interconnect IP claims to perform 5X faster physical convergence over manual refinements with fewer iterations. Source: Arteris

Arteris claims that FlexNoC 5 facilitates up to 5X faster physical convergence of the back-end physical design time and effort. That prepares the physically optimized NoC IP for physical synthesis and place-and-route implementations. FlexNoC 5 also expands support for Arm AMBA 5 protocols and IEEE 1685 IP-XACT, including a connectivity flow with Arteris Magillem for NoC integration with other SoC IP blocks.

Related Content

SoC Interconnect: Don’t DIY!Network on chip eases IP connectWhat is the future for Network-on-Chip?The network-on-chip interconnect is the SoCArteris spins packet-based network-on-chip IPHow physically aware interconnect IP bolsters SoC design由Voice of the EngineerICDesignColumn releasethank you for your recognition of Voice of the Engineer and for our original works As well as the favor of the article, you are very welcome to share it on your personal website or circle of friends, but please indicate the source of the article when reprinting it.“How physically aware interconnect IP bolsters SoC design”