EDA toolmakers prep for TSMC's N3E and N2 nodes

- ICDesign

- 2023-09-23 23:01:24

TSMC is bolstering its existing relationships with EDA companies by having their design tools certified for its N3E and N2 process nodes. Top EDA firms have announced a range of new certifications and collaborations with long-time partner TSMC coinciding with the TSMC 2023 North America Technology Symposium.

At the event, TSMC provided details about its 3-nm and 2-nm chip manufacturing process nodes called N3 and N2, respectively. While N3 is a baseline node, N3E is an enhanced version with reduced cost and better yield; it’s expected to be introduced in the second half of 2023. On the other hand, the N2 process node is on track for production in 2025.

The readiness of digital and custom/analog EDA flows and related process design kits (PDKs) for these advanced nodes will be crucial for TSMC in successfully launching these advanced process nodes. The trio of large EDA houses seem onboard, and below is a synopsis of their undertakings to prepare for the N3E and N2 process nodes.

CadenceCadence Design Systems claims its digital and custom/analog flows have been certified to support TSMC’s new Design Rule Manual (DRM) for the fab’s N3E and N2 nodes. The two companies have jointly delivered PDKs for N3E and N2 processes to facilitate mobile, artificial intelligence (AI), and hyperscale computing IC designs at these advanced nodes. Cadence has collaborated with TSMC on its complete RTL-to-GDS flow for use with TSMC’s N3E and N2 nodes.

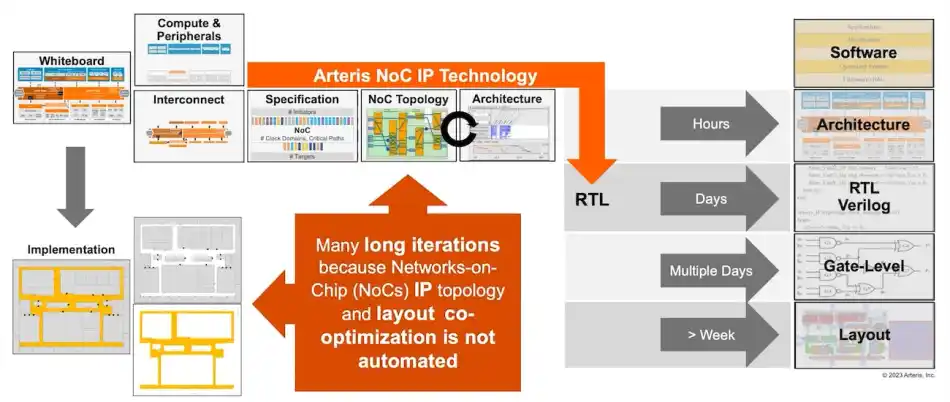

Figure 1 The digital implementation and signoff flow supports a variety of new design features, including native hybrid cell row optimization from synthesis to signoff engineering change order (ECO) for optimal power, performance and area (PPA), cell pin alignment, and connection support. Source: Cadence

Cadence has also announced the tapeout of its 16G UCIe 2.5D advanced package IP on TSMC’s N3E process node. The UCIe IP facilitates chiplet for die-to-die communication, which is becoming increasingly critical in AI and machine learning (ML), mobile, automotive, storage and networking applications, currently driving the need to move from monolithic integration to system-in-package (SiP) chiplets.

Siemens EDASiemens EDA’s Calibre nmPlatform tool for IC verification sign-off is fully certified for TSMC’s N3E and N2 processes. The two companies have also joined hands to certify Siemens’ mPower analog software for transistor-level electromigration and IR drop (EM/IR) sign-off for TSMC’s N3E process.

Figure 2 The Calibre platform for IC verification sign-off has been certified for TSMC’s N3E and N2 nodes. Source: Siemens EDA

Then there is the Analog FastSPICE platform for circuit verification of nanometer analog, RF, mixed-signal, memory, and custom digital circuits, which has achieved TSMC certification for the foundry’s N5A, N3E, and N2 processes. The EDA toolmaker has also upgraded its Tanner software, which helps IC designers lay out analog and mixed-signal ICs.

SynopsysSynopsys will deliver digital and custom design EDA flows on TSMC’s most advanced node, the N2 process, which leverages nanosheet transistors to offer up to 15% speed improvement at the same power or 30% power reduction at the same speed when compared with TSMC’s N3E process.

Sanjay Bali, VP of Strategy and Product Management for the EDA Group at Synopsys, acknowledged that the latest N2 process is pushing the edge of design physics. He said collaboration on N2 builds on the company’s certified EDA and IP solutions for TSMC’s 3-nm process technology with several dozen successful tapeouts. For example, Bali mentioned the in-chip process, voltage and temperature (PVT) monitor IP to boost N3 designs.

In October 2022, Synopsys provided details of its certifications for TSMC’s N3E process. Besides certified design flows and IP readiness, Synopsys is working closely with TSMC to scale physical verification in the cloud while using the Synopsys IC Validator product for N3E on the Synopsys Cloud software-as-a-service offering. That allows chip designers to access unlimited CPU capacity in the cloud for faster physical verification iterations.

Figure 3 IC Validator, a physical verification signoff solution, offers distributed processing scalability to over 4,000 CPU cores. Source: Synopsys

For AI-driven design enablement, Synopsys’ DSO.ai technology and Fusion Compiler have also been validated for multiple N3E test cases with better PPA and faster design closure.

Related Content

TSMC’s 3-nm Push Faces Tool StrugglesTSMC Details The Benefits of Its N3 NodeTSMC’s 3-nm progress report: Better than expectedTSMC approaching 1 nm with 2D materials breakthroughA closer look at TSMC’s 3-nm node and FinFlex technologyEDA toolmakers prep for TSMC's N3E and N2 nodes由Voice of the EngineerICDesignColumn releasethank you for your recognition of Voice of the Engineer and for our original works As well as the favor of the article, you are very welcome to share it on your personal website or circle of friends, but please indicate the source of the article when reprinting it.“EDA toolmakers prep for TSMC's N3E and N2 nodes”