Solar day lamp designs provide low

- LEDS

- 2023-09-23 23:13:35

In the first installment of this two-part series, we showed how to expand the usefulness of a solar day lamp by adding a motion-sensing function and a light sensor that adjusts the LED lamp to take advantage of any available light. This concluding segment introduces a simple way to support prioritized lighting, i.e. a controller that provides light to the most important areas of a building when power from the PV panels is limited.

In the previous designs we have explored, the LED arrays are wired such that they all turn on, regardless of how much power is available from the PV panel. As a result, all of the LED arrays will be dim during cloudy weather, as well as at dawn and dusk. One way to solve this problem would be to turn on the arrays selectively, based on the amount of power available from the PV panels. This “prioritized” arrangement ensures that at least one of the arrays will provide the brightest output possible, even when the sun is heavily obscured. The downside of this approach is that the other arrays will remain off until the sun becomes stronger.

A selectively-switched lighting system is useful in applications where the user can assign distinct priorities to different areas. A high priority area will always be the first to operate when some sunlight is available. Once additional power is available, the lights in a medium-priority area will be activated, although they may turn off again if the sunlight intensity drops below a certain threshold. The LED arrays in the lowest priority areas will be powered up last, after the first two arrays are operating, and additional power is available.

Wow the engineering world with your unique design: Design Ideas Submission Guide

Implementation

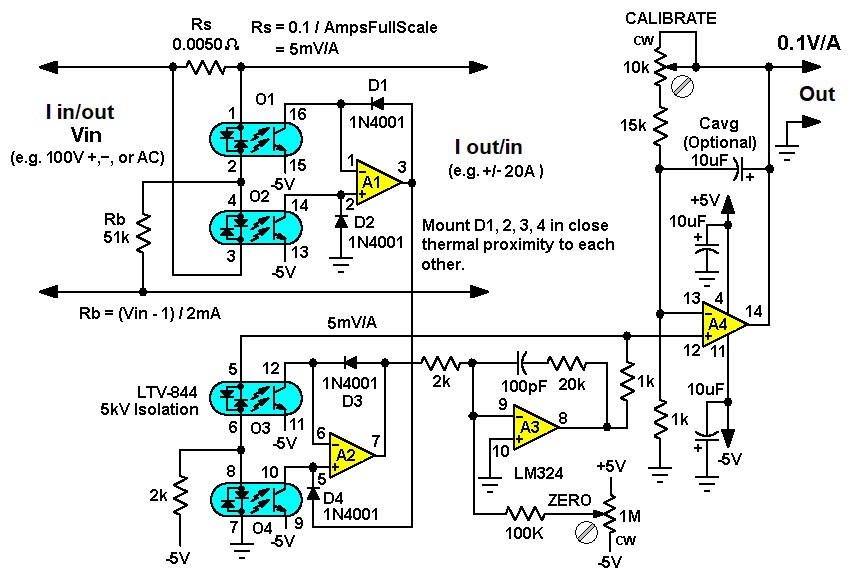

A circuit diagram of the prioritized lighting control system is shown in Figure 1. This is a variant of the basic solar day lamp topology powered by a single PV panel as described in my previous article. This basic design consists of three LED arrays having five LEDs each. For each array, a current limiting resistance of 10 Ω is included in series. These three arrays are connected to a single PV panel rated at 10W (peak).

In order to implement sequential control, a small current sensing resistance R6 (1.5 Ω) is introduced to the return path of the PV panel. Array A is connected to the panel through resistance R1. The value of R1 is reduced from 10 to 8.2 Ω because R6 is also in the series path. Array B is connected to the PV panel through R2 and Q1, a PNP transistor (2N4033). Similarly, array C is connected to the PV panel through R3 and Q2 (2N4033).

A dual comparator IC, U1 (LM393) is used to drive transistors Q1 and Q2. A Zener regulator consisting of D1 and R7 is used for supplying 5V to U1. Non-inverting terminals of the comparators are connected to potential divider circuits consisting of R13, R15 and R14, R16. Inverting terminals are connected to R6 through resistors R19 and R8. Resistors R11 and R12 are used to introduce small hysteresis.

Calculations

PV panel voltage at maximum power = Vmp = 17.4VPanel current at maximum power = Imp = 0.58 AMaximum current in each LED array = ILED = 0.58/3 = 0.193 AVoltage at pin 3 (when pin 1 is high)1 = 0.3VPanel current when the array B turns ON = 0.3/1.5 = 0.2 AVoltage at pin 5 (when pin 7 is high)2 = 0.527VPanel current when array C turns ON = 0.527/1.5 = 0.351 AAssuming all the three LED arrays are on, and sunlight intensity starts decreasing, the lower tripping point is calculated as follows:

Voltage at pin 5 (when pin 7 is low)3= 0.455VPanel current when array C turns off = 0.455/1.5 = 0.3 AVoltage at pin 3 (when pin 1 is low)4 = 0.26 APanel current when array B turns off = 0.26/1.5 = 0.173 ANotes:

1 Voltage is calculated by considering R11 and R15 are in parallel.2 Voltage is calculated by considering R12 and R16 are in parallel. 3 Voltage is calculated by considering R12 and R14 are in parallel. 4 Voltage is calculated by considering R11 and R13 are in parallel.

When either LED array B or C turns on, there is a sudden spike load current which causes a drop in the PV panel’s output voltage. Since the voltage sag could cause problems for the LED panels’ control electronics, a bulk capacitor C1 (75000 μF) is connected across the PV panel’s output terminals. Besides stabilizing the electronics’ supply voltage, keeping Vpv steady during short term variations in sunlight intensity also helps maintain the LED lamps’ output at a constant level.

Calculations for R2 and R3

Value of R2

When arrays A and B are fully ON, and array C is OFF:

Drop across R6 = 0.193 * 2 * 1.5 = 0.579VIf array B was directly connected to the PV panel through 10 Ω resistor, then drop across 10 Ω resistor would have been = 0.193 * 10 = 1.93VVoltage difference = 1.93 – 0.579 = 1.351VValue of R2 = 1.351/0.193 = 7 Ω (7.5 Ω is used)Value of R3

When arrays A, B, and C are fully ON:

Drop across R6 = 0.193 * 3 * 1.5 = 0.8685VIf array C was directly connected to the PV panel through 10 Ω resistor, then drop across 10 Ω resistor would have been = 0.193 * 10 = 1.93VVoltage difference = 1.93 – 0.8685 = 1.0651VValue of R3 = 1.0651/0.193 = 5.5 Ω (6.2 Ω is used)Photos of the actual PCB are shown in Figures 2 and 3.

Operation

When the sunlight intensity is low, only array A is ON because, it has been directly connected to the PV panel. In this condition, the voltage drop across R6 is smaller than the voltages set at non-inverting terminals of comparators. Hence, the comparator outputs are high and transistors Q1 and Q2 are OFF. As the sunlight intensity increases, the drop across R6 increases. When it exceeds voltage at pin 3 of comparator U1-1, its output goes low and Q1 turns ON.

As the sunlight intensity continues to increase, the drop across R6 eventually exceeds the voltage at pin 5 of the comparator U1. This causes its pin 2 to go low which turns Q2 on.

Changing the priority

If in any application, there is a need to change priority of the arrays, then, a simple three-pole, three-way switch can be inserted between the LED arrays and the resistors R1, R2, and R3, as shown in Figure 4. The three PV array terminals A, B, and C are connected to each of the switches, per the sequence shown in Figure 4. The poles P1, P2, and P3 are connected to resistors R1, R2, and R3 respectively. The rotary switch allows the user to select which array will be directly connected to the panel.

Vijay Deshpande recently retired after a 30-year career focused on power electronics and DSP projects, and now works mainly on solar PV systems.

Related articles:

Solar day lamp designs provide low-cost lighting solutions, Part 1Teardown: Motion-sensing LED lightingSolar LED lighting solutions for rural areasSolar day lamp designs use passive and active current-limiting circuitsSolar day lamp designs provide low由Voice of the EngineerLEDSColumn releasethank you for your recognition of Voice of the Engineer and for our original works As well as the favor of the article, you are very welcome to share it on your personal website or circle of friends, but please indicate the source of the article when reprinting it.“Solar day lamp designs provide low”