4 technologies that sum up imec’s sub

- ICDesign

- 2023-09-23 23:01:21

The sub-1 nm chip technology is already in sight, and imec’s ITF World event in Antwerp, Belgium provided a sneak peek into the major process nodes and transistor architectures serving sub-1 nm with timelines going all the way to 2036. According to a news report published in Tom’s Hardware, while transistor counts continue to double as per Moore’s Law trajectory, in imec’s view, the raw compute power needed for artificial intelligence (AI) and machine learning (ML) applications doubles approximately every six months.

Figure 1 The ITF World event in Antwerp, Belgium presented a roadmap for processor nodes and transistor architectures all the way to 2036. Source: imec

The event also highlighted that, besides cutting-edge silicon process nodes, the foundational issues are becoming increasingly sticky with each new generation of chips. Take, for example, the limitations of interconnect bandwidth that has severely lagged the computational capabilities of modern CPUs and GPUs. It’s hampering performance and limiting the effectiveness of extra transistors in these silicon devices.

The roadmap outlined at the event emphasizes continuous shrinking for the interconnects, which alongside 3D-stacked chip designs, will be crucial in paving the way for sub-1 nm silicon. Below are four prominent highlights that dominate the imec’s technology roadmap to sub-1 nm chips and will drive advancements of new types of interconnects and process nodes.

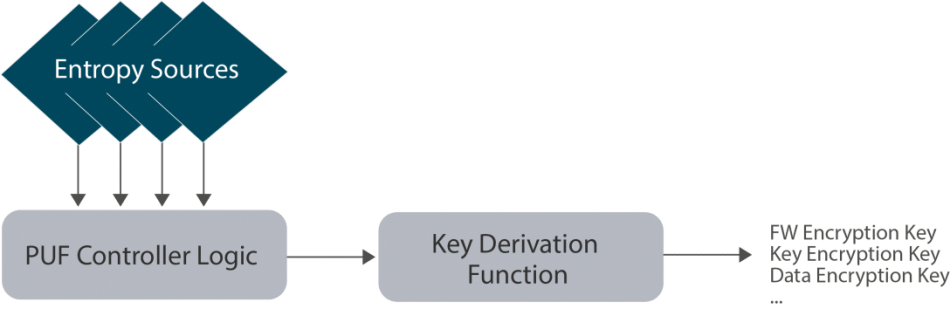

Forksheet and CFET technologiesWhile the standard FinFET transistors will last till 3-nm process nodes, the new gate all around (GAA) nanosheet manufacturing technology will take over the high-volume production of 2-nm chips in 2024. The GAA technology facilitates transistor density and performance improvements using the same drive current as multiple fins.

Additionally, GAA transistors significantly reduce leakage with channels surrounded entirely by a gate. According to imec’s roadmap, forksheet transistors, a denser version of GAA at its most basic level, will then take the baton from the 2-nm node and last through the 0.7-nm node.

Figure 2 The chip manufacturing technology could evolve from FinFET to CFET in nearly a decade. Source: imec

Next, imec anticipates that complementary FET (CFET) technology will further shrink the transistor footprint when it arrives around 2028 to create a 1-nm node, enabling more densely packed standard cell libraries. CFET transistors stack NMOS and PMOS on top of each other to facilitate higher density. The subsequent breakthroughs will encompass versions of CFET with atomic channels that will further improve the performance and scalability while reaching 0.5-nm and 0.2-nm nodes.

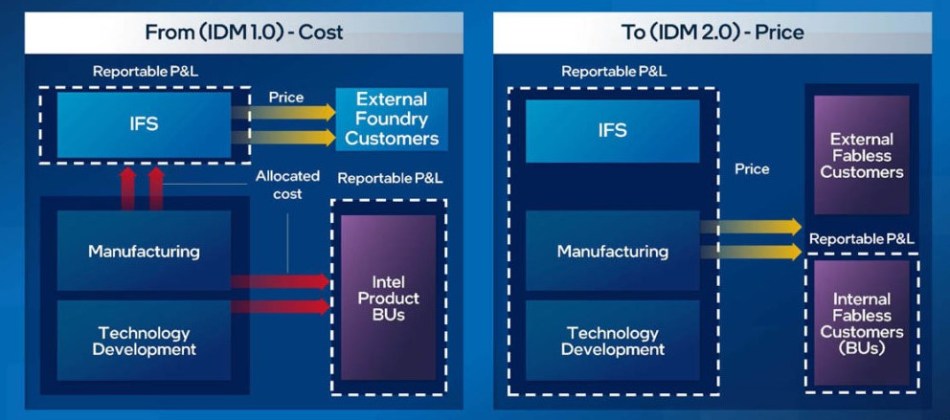

System technology co-optimization (STCO)System technology co-optimization (STCO) is a design methodology that reorganizes the IC design process by modeling the needs of the system and the target applications and then uses this know-how to make informed decisions while creating a chip. In short, it disintegrates functional units of a monolithic chip—such as cache, I/O, and power delivery—and splits them into separate units to optimize each unit for the required performance characteristics using different transistors.

Figure 3 Schematic representation of the STCO framework; STCO aims to break the performance, power, and density scaling barriers in future chip designs. Source: imec

One of the goals of disaggregating a standard chip design is to split cache and memory into their distinct layers in a 3D-stacked design. That, in turn, calls for a significant reduction in the complexity at the top of the IC stack. Here, imec proposes revamping the back end of line (BEOL) processes that focus on wiring the transistors together while enabling both communication (signals) and power delivery on a chip.

That brings us to the next important methodology in imec’s sub-1 nm silicon roadmap.

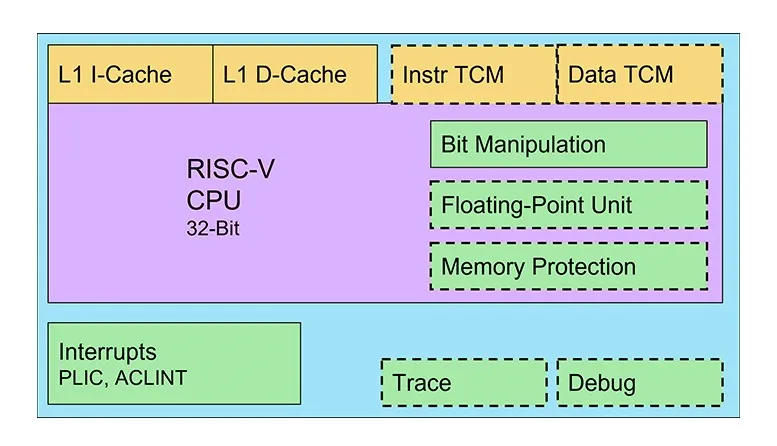

Backside power distribution networks (BPDN)Backside power delivery network (BPDN), which routes all power through the backside of the transistor, will actually debut with the advent of the 2-nm node in 2024. It separates the power circuitry and the data-carrying interconnects to improve voltage droop characteristics and allows denser signal routing on the top of the chip. Signal integrity is another beneficiary of the simplified routing that facilitates faster wires with reduced resistance and capacitance.

The BPDN technique partitions power delivery to the backside of the transistors, and data transmission interconnects remain in their traditional location on the other side. Next, moving the power delivery network to the bottom of the chip enables easier wafer-to-wafer bonding at the top of the die, making it possible to stack logic on memory.

Figure 4 Schematic representation of a BPDN implementation shows where nanosheets connect to the wafer’s backside with through-silicon vias (TSVs). Source: imec

While TSMC plans to implement BPDN in its high-volume production of the 2-nm node in 2026, Intel has plans to execute this technology in its 2-nm node to be launched in 2024. Intel, which calls its BPDN technology PowerVIA, is expected to provide more details about this technology later this year. Samsung, another key player in the nanometer race, is also expected to incorporate BPDN in its 2-nm chip manufacturing node.

CMOS 2.0CMOS 2.0—a prominent theme at imec’s this year’s event in Belgium—leans heavily on the BPDN methodology. It aims to break the chips into even smaller pieces while splitting caches and memories into their own units with distinct transistors. These smaller pieces are then stacked on other chip functions in a 3D arrangement.

Figure 5 The 3D functional partitioning of a system-on-chip (SoC) design breaks down the device into multiple levels of memory, logic, and I/O. Source: imec

It’s worth mentioning that 3D chip designs have already been launched; for instance, AMD’s second-generation 3D V-Cache stacks L3 memory on top of the processor to boost memory capacity. However, imec aims to take it to the next level by creating the entire cache hierarchy contained in its own layers. In other words, it will vertically stack L1, L2, and L3 caches on their own dies above the transistors comprising processing cores.

So, when each level of cache is created with the best-suited transistors for the task, older nodes can be used for SRAM for whom scaling has become very slow. That scaling problem, in turn, has led to caches that consume a higher percentage of the die, resulting in higher cost-per-MB. The use of 3D stacking will lead to much larger caches and will also address latency issues associated with larger caches.

Related Content

TSMC Details The Benefits of Its N3 NodeChina Struggles to Crack Chip ManufacturingTSMC Expansion in Arizona to Target 3-nm NodeTSMC approaching 1 nm with 2D materials breakthroughA closer look at TSMC’s 3-nm node and FinFlex technology4 technologies that sum up imec’s sub由Voice of the EngineerICDesignColumn releasethank you for your recognition of Voice of the Engineer and for our original works As well as the favor of the article, you are very welcome to share it on your personal website or circle of friends, but please indicate the source of the article when reprinting it.“4 technologies that sum up imec’s sub”