A sneak peek at chiplet standards

- Components

- 2023-09-27 10:44:56

The scaling of system-on-chip (SoC) architectures is hitting the wall, paving the way for die-to-die interconnect in heterogenous single-package systems commonly known as chiplets. But while these chiplet-optimized interconnect technologies are gaining significant traction, they are still in their infancy.

That makes chiplet interconnect standards crucial for the new multi-die semiconductors era. Below is a brief outline of three standards that are considered critical in the present evolution of chiplets. These standards will likely play a vital role in creating an open chiplet ecosystem.

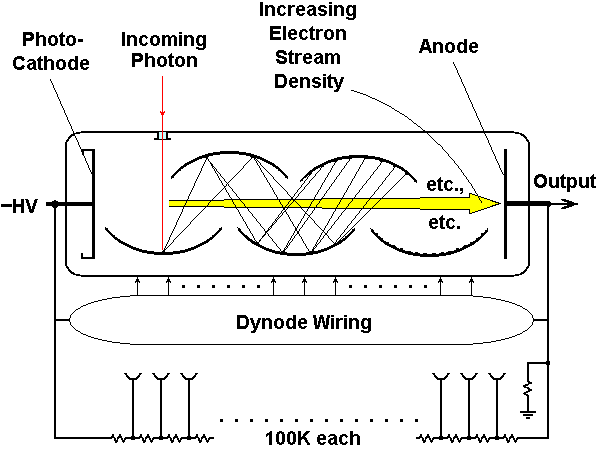

Bunch of WiresThe Bunch of Wires (BoW) interconnect technology defines an open and interoperable physical interface between a pair of dies inside a single package. It specifies a physical layer (PHY) optimized for SoC disaggregation to form the basis of multi-die interconnect for chiplets.

Eliyan’s founding CEO Ramin Farjadrad, who developed the original interconnect technology behind BoW, took it to the Open Compute Project (OCP) in 2018 for standardization. The technology was later adopted by the OCP as a chiplet interconnect scheme.

Figure 1 BoW is an open PHY specification for die-to-die (D2D) interconnect that offers parallel interfaces and can be implemented in organic laminate or advanced packaging technologies. Source: Eliyan

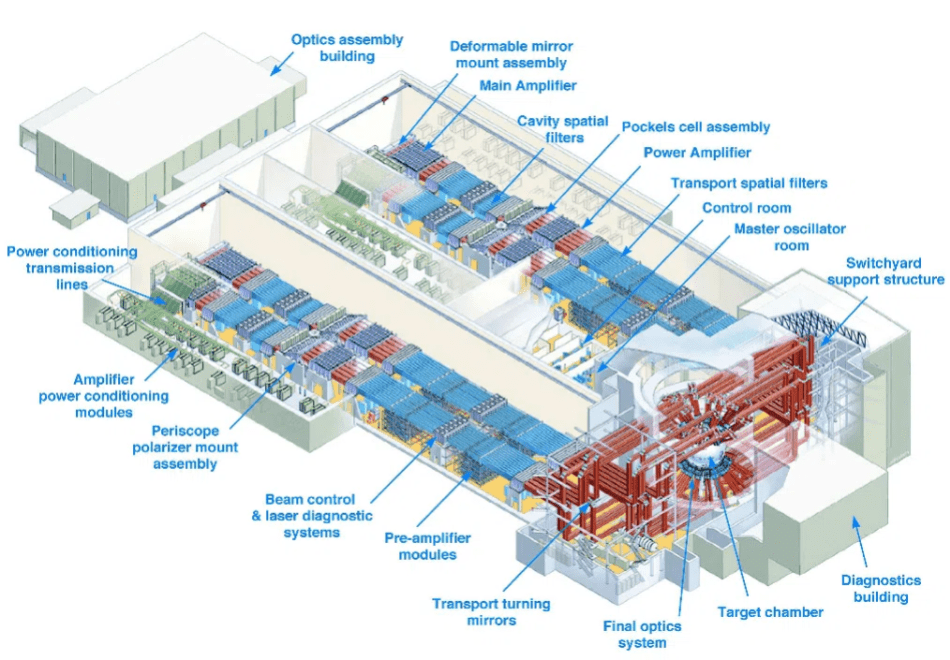

Universal Chiplet Interconnect Express (UCIe)The open industry standard for die-to-die connectivity was introduced in March 2022 by a consortium of over 80 companies, including semiconductor and packaging firms, foundries, and cloud services and IP suppliers. It’s an important step toward heterogeneous integration with multi-die systems and it’s aiming to create a new design ecosystem for semiconductor chiplets.

Figure 2 UCIe defines the key performance indicators for chiplets within a package. Source: UCIe

UCIe provides a plug-and-play interconnect at the package level and streamlines interoperability between dies on different process technologies from various suppliers. It’s based on the same signaling and clocking schemes and architecture basics as BoW interconnect and is currently available with the UCIe 1.1 specification.

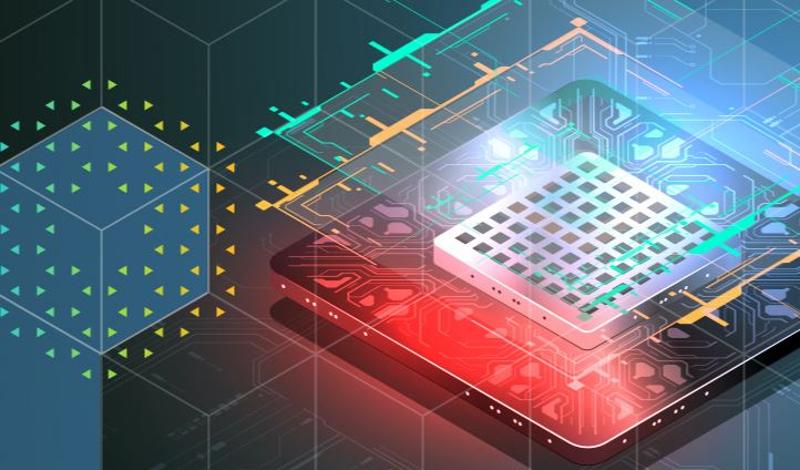

High Bandwidth Memory (HBM)Though not a chiplet standard specifically, it’s becoming a vital ingredient in chiplet designs for its ability to pack a larger number of memory chips into a smaller space. HBM enables various layers of memory chips to be stacked on top of each other by employing vertical channels called through-silicon vias (TSVs). It was originally designed to reduce the data travel distance between the memory and the processor.

Figure 3 HBM, originally designed for high-performance computing (HPC) applications, is acquiring a critical role in chiplets design ecosystem. Source: Eliyan

HBM, initially conceived for compute-intensive applications in data centers and cloud computing, is now highly relevant in chiplet designs for its ability to vertically stack DRAM chips on top of one another. That’s why several new chiplet solutions now support UCIe as well as HBM protocol.

Related Content

Chiplet interconnect handles 40 Gbps/bumpIP partnerships stir the world of FPGA chipletsChiplets Gain Popularity, Integration ChallengesChiplets advance one design breakthrough at a timeA sneak peek at chiplet standards由Voice of the EngineerComponentsColumn releasethank you for your recognition of Voice of the Engineer and for our original works As well as the favor of the article, you are very welcome to share it on your personal website or circle of friends, but please indicate the source of the article when reprinting it.“A sneak peek at chiplet standards”